**Ultra-Wideband Transceiver**

Rev. 1.2 — 29 September 2021 666312 Product short data sheet COMPANY PUBLIC

# **1** General description

The SR040 is a fully integrated single chip Impulse Radio Ultra-Wideband (IR-UWB) lowenergy transceiver IC compliant to IEEE 802.15.4/4z HRP UWB PHY (see [1] and [2]) and supports FiRa consortium MAC and PHY. It is designed for Ranging applications in an IOT environment. It can be used for 2-way ranging achieving an accuracy of ±10cm in non-line of sight; and one way ranging for Time Difference of Arrival.

# 2 Features and benefits

SR040 supports the following features.

- IEEE 802.15.4z HRP PHY compliant (see [1] and [2])

- Supports SHF UWB bands from 6.0 GHz to 8.5 GHz for worldwide use

- Programmable transmitter output power of up to 10.5 dBm peak

- Support of 128 MHz PRF (HPRF) mode, doubles available mean TX power compared to IEEE 802.15.4 (see [1])

- Supply voltage 1.8 V to 3.6 V

- · Configurable current limiter for applications with coin cell battery supply

- Supports 2-way ranging and TDoA

- Scrambled Timestamp Sequence (STS) generation compliant to NIST SP 800-90A (see [5])

- 6 mm x 6 mm 40-pin QFN package with 0.5 mm lead pitch and wettable flanks

- Based on ARM® Cortex-M33 with ARM® TrustZone (see [3] and [4])

- · FiRa ready MAC and PHY

- Built-in on-chip UWB FW (can be updated in the field)

- No custom programming required on processor

- SPI interface to host CPU

# 3 Applications

SR040 is targeted for following applications.

- · IoT applications with coin cell battery operation

- UWB trackers

- UWB tags

# 4 **Pinning information**

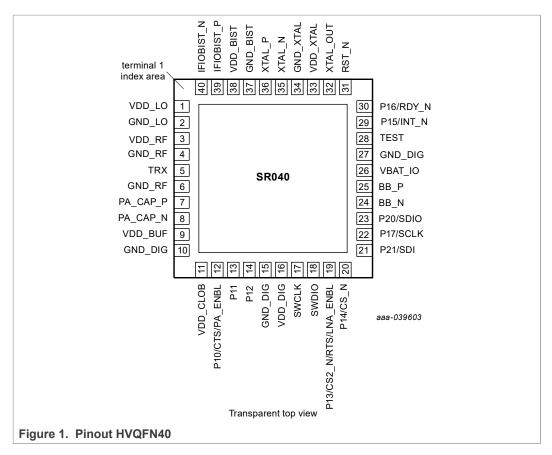

### 4.1 Pinning

SR040 is packaged in an HVQFN40.

#### 4.2 Pin description

| Table 1. SR040 pin description | Table 1. | SR040 | pin | description | ı |

|--------------------------------|----------|-------|-----|-------------|---|

|--------------------------------|----------|-------|-----|-------------|---|

| Symbol   | Pin | Description                                                                         |

|----------|-----|-------------------------------------------------------------------------------------|

| VDD_LO   | 1   | Power supply for local oscillator generation of the analog receiver and transmitter |

| GND_LO   | 2   | Ground                                                                              |

| VDD_RF   | 3   | Power supply for analog receiver and transmitter                                    |

| GND_RF   | 4   | Ground                                                                              |

| TRX      | 5   | Single-ended, RF receiver input and RF transmitter output                           |

| GND_RF   | 6   | Ground                                                                              |

| PA_CAP_P | 7   | External decoupling capacitor                                                       |

| PA_CAP_N | 8   | External decoupling capacitor                                                       |

| VDD_BUF  | 9   | Internally connected to VBAT_IO, supply for global LDO and PA                       |

SR040 Product short data sheet COMPANY PUBLIC

**Ultra-Wideband Transceiver**

| Symbol                             | Pin | Description                                                                                                        |

|------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------|

| GND_DIG                            | 10  | Ground (digital)                                                                                                   |

| VDD_GLOB                           | 11  | Output voltage of the global LDO                                                                                   |

| P10 / CTS / PA_ENBL <sup>[1]</sup> | 12  | Optional external wake source                                                                                      |

| P11 <sup>[1]</sup>                 | 13  | N/A                                                                                                                |

| P12 <sup>[1]</sup>                 | 14  | N/A                                                                                                                |

| GND_DIG                            | 15  | Ground (digital)                                                                                                   |

| VDD_DIG                            | 16  | Power supply for digital domain                                                                                    |

| SWCLK                              | 17  | Debug interface. N/A                                                                                               |

| SWDIO                              | 18  | Debug interface. N/A                                                                                               |

| P13 <sup>[1]</sup>                 | 19  | Test point                                                                                                         |

| P14 / CS_N <sup>[1]</sup>          | 20  | GPIO CS_N - Chip Select (active low); input in SPI Slave operation                                                 |

| P21 / SDI <sup>[1]</sup>           | 21  | GPIO SDI - Data input for SPI full duplex operation                                                                |

| P17 / SCLK <sup>[1]</sup>          | 22  | GPIO SCLK - Data clock for SPI operation; input in SPI Slave operation                                             |

| P20 / SDIO <sup>[1]</sup>          | 23  | GPIO SDIO - Data I/O for SPI operation; output in full duplex operation; input/<br>output in half-duplex operation |

| BB_N                               | 24  | External decoupling capacitor                                                                                      |

| BB_P                               | 25  | External decoupling capacitor                                                                                      |

| VBAT_IO                            | 26  | Power supply for digital I/Os and power supply for the chip via current limiter                                    |

| GND_DIG                            | 27  | Ground (digital)                                                                                                   |

| TEST                               | 28  | Test pin (must be connected to ground in the application)                                                          |

| P15 / INT_N <sup>[1]</sup>         | 29  | GPIO INT_N - Interrupt output (active low) in 6-wire SPI operation                                                 |

| P16 / RDY_N <sup>[1]</sup>         | 30  | GPIO RDY_N - Ready output (active low) in 6-wire SPI operation                                                     |

| RST_N                              | 31  | Reset input (active low), internal pull-up resistor                                                                |

| XTAL_OUT                           | 32  | N/A                                                                                                                |

| VDD_XTAL                           | 33  | Power supply for XTAL                                                                                              |

| GND_XTAL                           | 34  | Ground                                                                                                             |

| XTAL_N                             | 35  | External crystal                                                                                                   |

| XTAL_P                             | 36  | External crystal                                                                                                   |

| GND_BIST                           | 37  | Ground                                                                                                             |

| VDD_BIST                           | 38  | Power supply for BIST, ADC, DAC, system clock generation                                                           |

| IFIOBIST_P                         | 39  | N/A, Ground                                                                                                        |

| IFIOBIST_N                         | 40  | N/A, Ground                                                                                                        |

#### Table 1. SR040 pin description...continued

[1] Unused GPIO pins should be left open.

# 5 Functional description

This chapter provides high-level information on SR040 architecture and subsystems along with functional usage. The SR040 can be connected to a host controller through physical interface of SPI. The SR040 supports&#160operation in 3 V power supply. SR040 has one RX and one TX.

#### 5.1 CPU subsystem

SR040 is based on ARM<sup>®</sup> Cortex<sup>®</sup>-M33 processor (see [3]) and implements the ARM<sup>®</sup> TrustZone extension (see [4]). FiRa MAC and PHY FW is implemented on ARM<sup>®</sup> Cortex<sup>®</sup>-M33. UWB chip provides SPI interface toward host processor, which allows driving different UWB features from connected host.

#### 5.1.1 Serial peripheral interface (SPI)

A single serial peripheral interface (SPI) block is provided. It supports the following key features.

- SPI data rate up to 10 MHz supported

- SPI slave operation supported

- Data transmissions of 1 to 16 bit supported directly. Larger frames supported by software

- The SPI building block supports separate transmit and receive FIFO buffers with 8 entries each with 16-bit width

- The device supports wake-up from power-saving modes through events on the SPI interface

| Pin         | Туре  | Function | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P17 / SCLK  | I/O   | SCK      | Serial Clock for SPI. SCK is a clock signal used to synchronize the transfer<br>of data. It is driven by the master and received by the slave. When the SPI<br>interface is used, the clock is programmable to be active high or active-low.<br>SCK only switches during a data transfer. It is driven whenever the Master<br>bit in CFG equals 1, regardless of the state of the Enable bit. |

| P21 / SDI   | Input | MOSI     | Data input when SPI is a slave in 4-wire operation, it clocks in serial data from this signal.                                                                                                                                                                                                                                                                                                |

| P20 / SDIO  | I/O   | MISO     | Data output when SPI is a slave in 4-wire operation.                                                                                                                                                                                                                                                                                                                                          |

| P14 / CS_N  | I/O   | SSEL0    | Slave Select 0 for SPI. By default, this signal is active low but can be selected to operate as active high. When the SPI is a slave, any SSEL in an active state indicates that this slave is being addressed. The SSEL pin is driven.                                                                                                                                                       |

| P13 / CS2_N | I/O   | SSEL1    | Not supported                                                                                                                                                                                                                                                                                                                                                                                 |

|             |       | SSEL2    | Not supported                                                                                                                                                                                                                                                                                                                                                                                 |

|             |       | SSEL3    | Not supported                                                                                                                                                                                                                                                                                                                                                                                 |

Table 2. SPI Pin description

In addition to the 4-wire mode, two additional and optional control lines are provided (resulting in the 6-wire mode). These are the RDY\_N (Ready not) and the INT\_N (Interrupt not).

#### **Ultra-Wideband Transceiver**

The RDY\_N signal handshakes the CS\_N (generated from the host) in order to ensure that the SPI transfer will be successful. CS\_N can be understood as a request to send (RTS) and the RDY\_N as clear to send (CTS). Using the RDY\_N signal is optional, and the host can always rely on waiting some predefined time to transmit a command or read a response. The RDY\_N signal is activated (active low) always after CS\_N activation and deactivated after CS\_N deactivation. When the host (SPI master) accidentally transmits a command while the RDY\_N is not activated, the SR040 will ignore the transfer.

The purpose of the INT\_N signal is to inform the host that there are data to be read from the device, or an event has occurred which needs to be inspected by the host. Using the INT\_N signal is optional, and the host can always rely on polling the SR040 for its status and act accordingly. The INT\_N signal is active low. It can be activated at any time, because events that trigger the INT\_N are asynchronous and cannot be foreseen. The INT\_N is active as long as a pending event isn't read out. INT\_N is cleared after the SPI transmission was started by the host activating CS\_N and the SR040 handshaking this by activating RDY\_N. If another event is pending, INT\_N is reactivated.

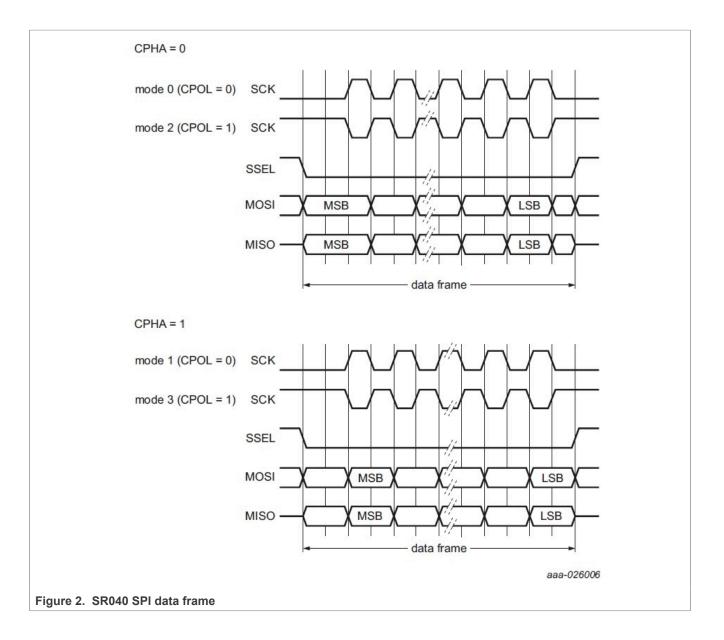

SPI interfaces typically allow configuration of clock phase and polarity. These are referred as numbered SPI modes, as described in <u>Table 3</u> and <u>Figure 2</u>. CPOL and CPHA are configured by internal CFG register. CPHA refers to the Clock Phase option and CPOL refers to the Clock Polarity.

| CPOL | СРНА | SPI<br>Mode | Description                                                                                                                                                                | SCK Rest<br>state | SCK data<br>change<br>edge | SCK data<br>sample<br>edge |

|------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|----------------------------|

| 0    | 0    | 0           | The SPI captures serial data on the first clock transition<br>of the transfer (when the clock changes away from the<br>rest state). Data is changed on the following edge. | Low               | Falling                    | Rising                     |

| 0    | 1    | 1           | The SPI changes serial data on the first clock transition<br>of the transfer (when the clock changes away from the<br>rest state). Data is captured on the following edge. | Low               | Rising                     | Falling                    |

| 1    | 0    | 2           | Same as mode 0 with SCK inverted.                                                                                                                                          | High              | Rising                     | Falling                    |

| 1    | 1    | 3           | Same as mode 0 with SCK inverted.                                                                                                                                          | High              | Falling                    | Rising                     |

Table 3. SPI mode summary

**Ultra-Wideband Transceiver**

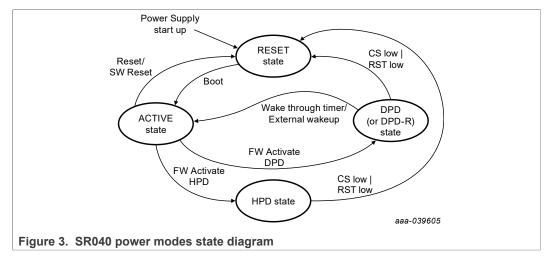

### 5.2 Power management

#### 5.2.1 Modes of operation

The device supports operation in a 3 V environment supporting the following supply use cases:

- Device and digital interface supplied with regulated 3 V (3.3 V) supply

- Digital signaling between all devices in the system is done at 3 V (3.3 V) level.

- Device and digital interface supplied with a 3 V battery

- Digital signaling between all devices in the system is done at battery voltage level.

MCU and SR040 use same Vbat, then no level translators are required.

- An energy storage capacitor is required to deliver the required peak current during frame reception and frame transmission.

#### 5.2.2 Power modes state diagram

Figure 3 shows different power states and transition of those power states.

#### 5.2.3 Current limiter

The current limiter is intended for applications with coin cell battery supply, to maximize the lifetime of the battery. It minimizes battery stress by limiting the maximal current drawn by the IC. The current limit is configurable by SW.

# 6 Recommended operating conditions

| Table 4. Operating conditions       |                                           |      |     |      |      |

|-------------------------------------|-------------------------------------------|------|-----|------|------|

| Parameter                           | Conditions                                | Min  | Тур | Мах  | Unit |

| Frequency range                     | Operating frequency Ch5, Ch6, Ch8 and Ch9 | 6.24 | -   | 8.24 | GHz  |

| Operating Temperature               | All specification parameters fulfilled    | -30  | +25 | +85  | °C   |

| Supply voltage range <sup>[1]</sup> | Device fully functional                   | 1.8  | -   | 3.6  | V    |

#### Table 4. Operating conditions

[1] TX PA peak power shall not be set higher than 9dBm between 1.8V and 2.4V

SR040

**Ultra-Wideband Transceiver**

# 7 Glossary

| Table 5. Glossary |                              |

|-------------------|------------------------------|

| ADC               | Analog to Digital Converter  |

| BIST              | Built-in Self-Test           |

| DAC               | Digital to Analog Converter  |

| DPD               | Deep Power Down              |

| HPD               | Hard Power Down              |

| PER               | Packet Error Rate            |

| RF                | Radio Frequency              |

| RX                | Receiver                     |

| SHF               | Super High Frequency         |

| SPI               | Serial Peripheral Interface  |

| STS               | Scrambled Timestamp Sequence |

| SWD               | Serial Wire Debug            |

| TDoA              | Time Difference of Arrival   |

| ТоҒ               | Time of Flight               |

| ТХ                | Transmitter                  |

| TRX               | Transmitter Receiver         |

| UWB               | Ultra Wideband               |

### 8 References

- [1] IEEE Std 802.15.4<sup>™</sup>-2015 (Revision of IEEE Std 802.15.4-2011) IEEE Standard for Local and metropolitan area networks – Part 15.4: Low-Rate Wireless Personal Area Networks (LR-WPANs). IEEE Computer Society Sponsored by the LAN/MAN Standards Committee. <u>https://standards.ieee.org/</u>

- [2] **IEEE Std 802.15.4z<sup>™</sup>-D08** (Draft Revision of IEEE Std 802.15.4-2015) Amendment: Enhanced Ultra Wide-4 Band (UWB) Physical Layers (PHYs) and Associated Ranging Techniques <u>https://www.techstreet.com/ieee/standards/ieee-p802-15-4z?</u> gateway\_code=ieee&vendor\_id=7291&product\_id=2087572

- [3] <u>ARM<sup>®</sup> Cortex<sup>®</sup>-M33 Processor Technical Reference Manual</u> Rev. r0p2

- [4] <u>ARM<sup>®</sup> TrustZone</u>

- [5] NIST Special Publication 800-90A Revision 1 2015. Recommendation for Random Number Generation Using Deterministic Random Bit Generators

SR040

# 9 Revision history

| Document ID    | Release date                                                                                                                                                                                                                                                              | Data sheet status                                              | Change notice           | Supersedes   |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------|--------------|

| 666312         | 2021-09-29                                                                                                                                                                                                                                                                | Product short data sheet                                       | -                       | 666311       |

| Modifications: | Update <u>Section 7</u>                                                                                                                                                                                                                                                   |                                                                |                         |              |

| 666311         | 2021-06-11                                                                                                                                                                                                                                                                | Product short data sheet                                       | -                       | 666310       |

| Modifications: | <ul> <li>Update in <u>Section</u></li> <li>Updates <u>Section</u></li> <li>Updates in <u>Table</u></li> <li>Updates in <u>Section</u></li> <li>Updates in <u>Section</u></li> <li>Deleted Sections</li> <li>Added <u>Section 5.1</u></li> <li>Glossary updated</li> </ul> | 2<br>1<br>on 5.1<br>"5.2.2 Power supply states" and "5.<br>2.2 | 2.2.1 State Diagram and | Power modes" |

| 666310         | 2021-03-22                                                                                                                                                                                                                                                                | Product short data sheet                                       | -                       | -            |

| Modifications: | <ul> <li>Initial version</li> </ul>                                                                                                                                                                                                                                       |                                                                | 1                       |              |

#### Table 6. Revision history

# **10** Legal information

## 10.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

# 10.2 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

# **10.3 Disclaimers**

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

$\ensuremath{\mathsf{Applications}}$  — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

SR040

Ultra-Wideband Transceiver

SR040

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements

concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 10.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile — are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

**Bluetooth** — the Bluetooth wordmark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by NXP Semiconductors is under license.

SR040

Ultra-Wideband Transceiver

# **Tables**

| Tab. 2. | SR040 pin description2<br>SPI Pin description4<br>SPI mode summary5 |  |  |  |

|---------|---------------------------------------------------------------------|--|--|--|

| Figures |                                                                     |  |  |  |

| Fig. 1. | Pinout HVQFN40       | 2 |

|---------|----------------------|---|

| Fig. 2. | SR040 SPI data frame | 6 |

Fig. 3. SR040 power modes state diagram ......7

Tab. 4. Tab. 5.

Tab. 6.

Operating conditions ......7

Revision history ......10

# Contents

| 1     | General description               | 1    |

|-------|-----------------------------------|------|

| 2     | Features and benefits             |      |

| 3     | Applications                      | 1    |

| 4     | Pinning information               | 2    |

| 4.1   | Pinning                           | 2    |

| 4.2   | Pin description                   | 2    |

| 5     | Functional description            | 4    |

| 5.1   | CPU subsystem                     | 4    |

| 5.1.1 | Serial peripheral interface (SPI) | 4    |

| 5.2   | Power management                  | 7    |

| 5.2.1 | Modes of operation                | 7    |

| 5.2.2 | Power modes state diagram         | 7    |

| 5.2.3 | Current limiter                   | 7    |

| 6     | Recommended operating conditions  | 7    |

| 7     | Glossary                          | 8    |

| 8     | References                        | 9    |

| 9     | Revision history                  | . 10 |

| 10    | Legal information                 | 11   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 29 September 2021 Document number: 666312